即可将网页分享至朋友圈

近日,我校信息与通信工程学院文光俊教授团队与美国德州大学奥斯汀分校(University of Texas at Austin)孙楠教授团队合作,在集成电路领域国际旗舰期刊IEEE Journal of Solid-State Circuits上发表了题为“A 0.029-mm² 17-fJ/Conversion-Step Third-Order CT ΔΣ ADC With a Single OTA and Second-Order Noise-Shaping SAR Quantizer”(一款基于单OTA和二阶噪声整形SAR量化器的0.029mm²每步转换能耗17飞焦耳的三阶连续时间ΔΣ模数转换器)的研究论文。文光俊教授指导的博士研究生刘佳欣为论文第一作者,电子科技大学信息与通信工程学院为第一作者单位。

据悉,这是文光俊教授团队第二次在该期刊上发表研究论文。包括该篇论文在内,我校作为第一作者单位已在JSSC上发表了7篇论文,其中电子科学与工程学院康凯教授团队3篇及李强教授团队1篇、通信抗干扰技术国家级重点实验室胡剑浩教授团队1篇。JSSC自1966年创刊以来,共发表论文12300余篇,大陆地区仅在该刊上发表论文50余篇。

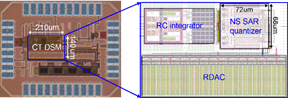

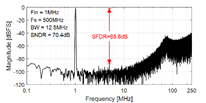

(a)芯片显微照片与版图 (b)芯片实测频谱特性

作者在论文中提出了一种新型混合结构连续时间ΔΣ ADC架构,其将无源噪声整形SAR ADC作为连续时间ΔΣ ADC的量化器,融合了连续时间和离散时间架构的优势;仅需要一个OTA即实现了三阶噪声整形,显著降低了ADC电路复杂度、功耗和芯片面积;在提高ADC稳定性的同时保留了抗混叠滤波特性。本论文提出的无源噪声整形SAR量化器完全基于开关电容电路实现,有效地将带内量化噪声、比较器噪声等非理想因素降低了24dB;与经典SAR ADC 相比,仅增加了两个开关、两个电容和两个比较器的差分输入对,结构简单;与已有的同类无源噪声整形SAR ADC 相比,有效减小了无源积分通路的衰减,显著降低了ADC 的等效输入噪声,在相同的热噪声预算条件下将电路中总电容面积降低2.4倍、DAC电容面积降低5倍、比较器功耗降低40%。ADC芯片采用40nm CMOS工艺制成,芯片实测的能效品质因数为每步转换能耗17飞焦耳,为目前世界一流水平;设计的ADC芯片具有面积小、稳定性高、功耗低等优点,在物联网、无线通信等信号处理领域具有广阔的应用前景。

刘佳欣是信息与通信工程学院2013级博士生,2015-2017年公派到美国德州大学奥斯汀分校孙楠教授团队联合培养,2018年12月博士毕业后到清华大学作博士后,主要研究方向为模拟与混合信号集成电路技术研究。除此篇论文以外,该博士生还在电路与系统领域的顶级期刊(IEEE Transactions on Circuits and Systems I: Regular Papers)、顶级国际固态电路会议(IEEE International Solid-State Circuits Conference、IEEE Symposium on VLSI Technology and Circuits)上发表多篇研究论文。在校期间获得过国家奖学金、国睿一等奖学金、一等学业奖学金、“芯原杯”电路设计大赛一等奖。

文光俊教授领导的射频集成电路与系统研究中心科研团队主要从事集成电路、RFID、卫星导航、传感网及物联网、无线输能及数能同传系统等技术研究,开发出自主知识产权的北斗导航终端射频芯片、超高频RFID标签芯片、多协议超高频RFID读写器、蜂窝物联网系统等系列产品,部分实现了产业化应用;已在Nature Communications、IEEE Commun. Surv. Tut.、Adv. Opt. Mater.、Phys. Rev. Appl.、IEEE JSSC、IEEE Trans CAS/MTT/AP、APL、Optics Express等国际著名期刊和VLSI、CELO、IEEE IMS/APS等国际会议上发表论文500余篇,其中SCI收录论文200余篇;获得授权发明专利50余项、省部级科技奖4项,获中国电子教育学会“优秀博士学位论文”1篇。

论文链接:https://ieeexplore.ieee.org/document/8543627

编辑:庄志东 / 审核:罗莎 / 发布:陈伟