即可将网页分享至朋友圈

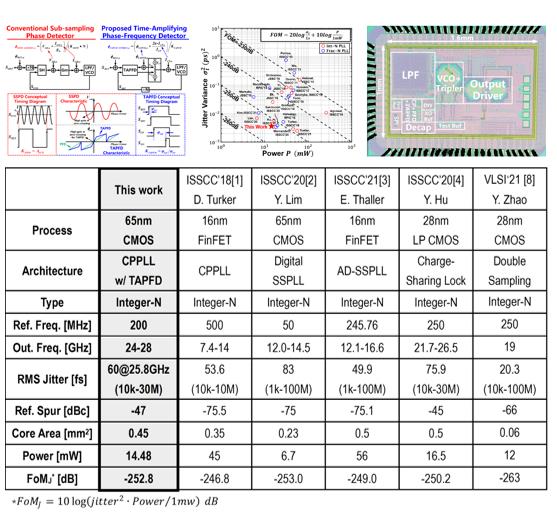

近日,电子科学与工程学院王政教授团队在具有“芯片奥林匹克”之称的IEEE国际固态电路会议(ISSCC 2022)上发表了其团队在高性能锁相环频率综合器领域的突破性研究成果A 25.8GHz Integer-N PLL with Time-Amplifying Phase-Frequency Detector Achieving 60fsrms Jitter, -252.8dB FoMJ, and Robust Lock Acquisition Performance。该项技术打破了传统电荷泵设计中噪声-功耗的折衷关系,将电荷泵锁相环的性能优值(Figure-of-merit, FoM)推进到了-250dB以下(-252.8dB)。电子科技大学为该论文唯一单位,王政教授指导的博士生耿新林为第一作者,王政教授为通讯作者。

无线通信系统需要一个稳定的频率源来实现信号的调制解调、时钟恢复、频率合成以及时钟偏移消除等功能。随着未来通信系统对传输速率、调制阶数的要求越来越高,如何实现更低的相位噪声和抖动性能成为了频率源芯片领域的亟需突破的瓶颈问题。针对这一挑战,该论文提出了一种基于时间放大鉴频鉴相器(Time-amplifying Phase Frequency Detector, TAPFD)的电荷泵锁相环频率综合器,为锁相环设计提供了一种新的设计思路。与国际上流行的低相噪亚采样鉴相器(Sub-sampling Phase Detector, SSPD)相比,TAPFD在提高输入-输出相位误差增益的同时保留了传统鉴频鉴相器的频率鉴别能力,因而在通过高增益抑制锁相环带内噪声的同时避免了SSPD潜在的锁定问题,实现了60fs jitter, 2.6us锁定时间的优秀性能。

王政教授团队(SICS Lab)面向下一代超高速无线通信、太赫兹成像等应用,长期致力于硅基毫米波太赫兹集成电路与系统的研究,解决晶体管在接近其最高截止频率时面临的一系列挑战,在理论模型层面、设计方法层面、和电路架构层面开展创新性研究工作。团队承担了包括国家自然科学基金重点项目在内的十余项纵向/横向科研项目,多项研究成果发表在包括ISSCC在内的集成电路领域顶级会议和期刊上。近年来指导学生多次获得包括全国大学生集成电路创新创业大赛IEEE杯最高奖等在内的多个奖项。

相关链接:

ISSCC是“IEEE International Solid-State Circuits Conference”的缩写,国际固态电路会议,是世界学术界和企业界公认的集成电路设计领域最高级别会议,被认为是集成电路设计领域的“世界奥林匹克大会”。始于1953年的ISSCC通常是各个时期国际上最尖端固态电路技术最先发表之地,历史上入选ISSCC的论文都代表着当前全球顶尖水平,众多集成电路历史上里程碑式的发明都是在该会议上首次披露。

编辑:李国一 / 审核:林坤 / 发布:陈伟