即可将网页分享至朋友圈

近日,集成电路科学与工程学院功率集成技术实验室明鑫教授研究小组在集成电路领域顶级期刊《IEEE Journal of Solid-State Circuits (JSSC)》发表了在低压差线性稳压器(Low-Dropout Regulator,LDO)领域关于低功耗-快速瞬态技术的突破性研究成果。

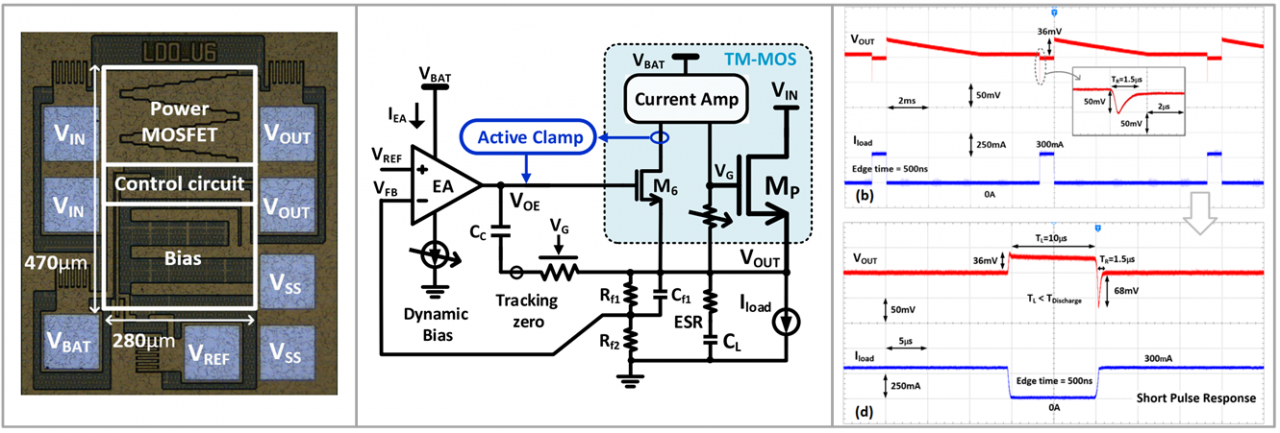

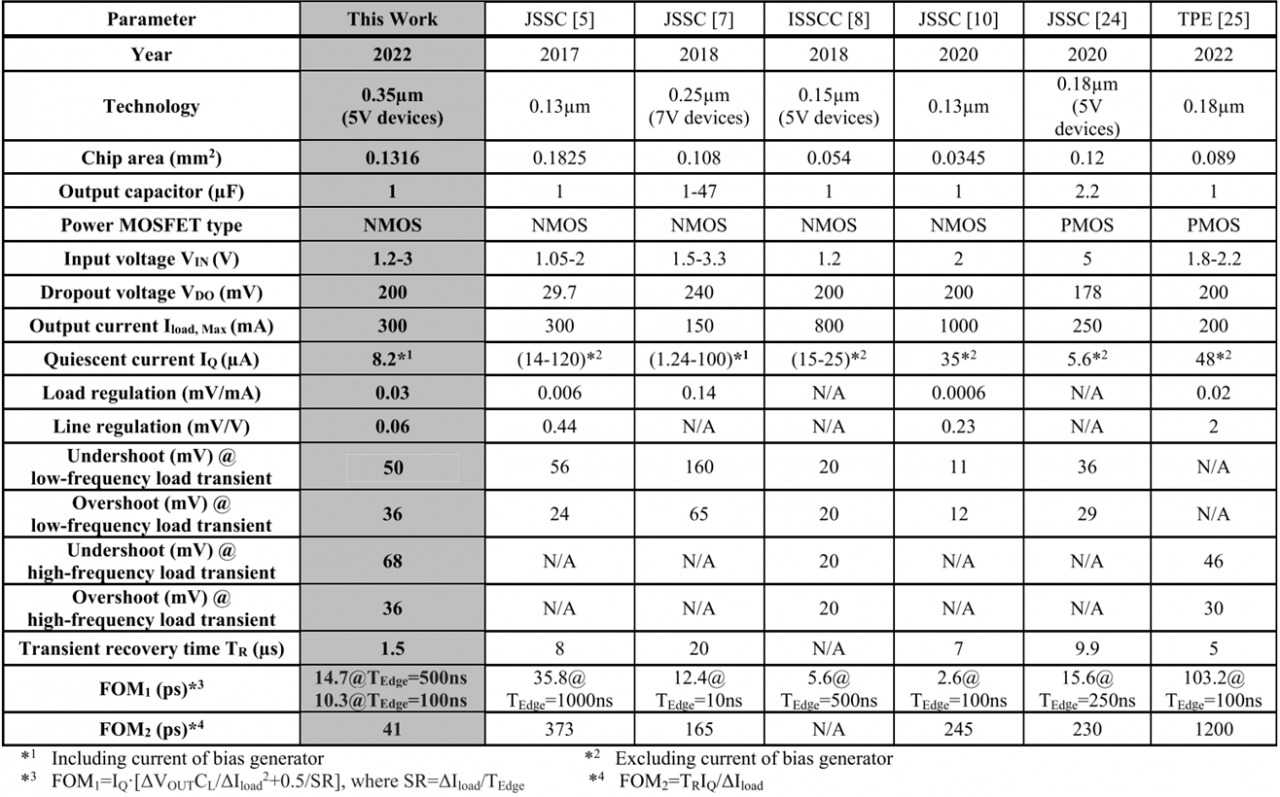

该项技术可显著提升智能手机和无人机等高速拍照性能,采用先进的负载电流回收和有源钳位控制架构,静态功耗仅为8.2μA,可同时处理高低频负载瞬态跳变,将LDO瞬态品质因数(Figure-of-merit, FoM)压缩至41ps,首次实现大电流LDO业界最快高频跳载能力(10μs间隔)。明鑫教授为第一/通讯作者,指导的硕士研究生邝建军为第二作者。

移动设备一般采用锂电池(3.6-4.5V)级联多路Buck变换器+LDO的点式供电架构:Buck用于高效率降压,而LDO将Buck输出纹波电压转换为稳定供电电源。LDO设计面临关键挑战:(1)对于Flash Memory等输入电压较低(VIN=1V)、负载电流较大(Iload>300mA)的应用,LDO通常采用N型功率管来减小芯片面积以及优化瞬态性能。由于NMOS-LDO特有的驱动死区问题,高频负载跳变会显著恶化瞬态性能;(2)LDO的静态功耗需要最小化以延长电池使用时间,然而对低功耗的追求恶化了LDO的瞬态、电源抑制比等关键性能。

基于上述挑战,明鑫教授研究小组研究设计了一种静态电流回收、近零驱动死区的LDO控制架构:a. 提出跨导增强MOS的全新缓冲器架构,在有效驱动功率管栅电容的同时,静态功耗完全被负载回收;b. 有源钳位电路用于在输出电压过冲时,快速精确钳位误差放大器的输出电压下限,将LDO驱动死区减小为近零状态。借助上述技术,设计LDO在仅消耗8.2μA的条件下,实现了41ps的品质因数,同时高频瞬态时的输出电压波动较低频瞬态相比仅增加了40%。和国际先进研究水平相比,在高速低功耗响应上具有明显优势。

明鑫教授,功率半导体顶会ISPSD TPC、华为-电子科大功率电子技术联合实验室技术委员会委员,其研究小组专注于高频高功率密度集成电路与系统研究,包括低压大电流供电、智能功率器件驱动、高密度隔离电源和片上LDO等。主持/承担多项国家重点研发计划课题、自然科学基金项目,以及华为、华润微等业界重要横向课题。在IEEE JSSC、TCAS I/TCAS II、TPE、TIE、ISPSD和CICC等电路旗舰期刊和顶尖会议上发表论文20余篇。学生广泛就职于华为、MPS、士兰微、中国电科集团、Silergy、思瑞浦、圣邦微等集成电路重点企事业单位。

论文链接:https://ieeexplore.ieee.org/document/10233212

编辑:刘瑶 / 审核:王晓刚 / 发布:陈伟